Difference between revisions of "StrichLux/IO-DMX"

From Hackstrich

(Dormantizing for now.) |

|||

| (7 intermediate revisions by the same user not shown) | |||

| Line 2: | Line 2: | ||

== Project Status == | == Project Status == | ||

| + | * 2012-09-09: Putting on hold for now, other modules have priority. | ||

| + | * 2012-05-31: Fixed a bunch of issues introduced in the rearchitecting, transmission now works properly again. Started working on the architecture for the DMX receiver module. | ||

| + | * 2012-05-28: Rearchitected the code to support transmission or reception modules being activated via a series of muxes. | ||

| + | * 2012-05-16: If I disable the tx_en functionality, transmission now fully works! Need to troubleshoot tx_en further, and get reception done. | ||

| + | * 2012-05-01: Still not able to get it working on real hardware. Attempted to get JTAG working, found TDI/TDO pins were connected wrong, green-wired it and can now connect to the chip via JTAG. Will do more troubleshooting tomorrow. | ||

| + | * 2012-04-29: Spent a few hours finding/fixing bugs, simulator now looks really good. Will test on real hardware this week. | ||

* 2012-04-23: Worked more on the code for the CPLD, it's getting stuck somewhere in the state machine and hanging outputting a high level. Need to troubleshoot more in the simulator. | * 2012-04-23: Worked more on the code for the CPLD, it's getting stuck somewhere in the state machine and hanging outputting a high level. Need to troubleshoot more in the simulator. | ||

* 2012-04-20: Programmed CPLD and it successfully blinks the status LED green/red! Also started working on the controller code. | * 2012-04-20: Programmed CPLD and it successfully blinks the status LED green/red! Also started working on the controller code. | ||

| Line 15: | Line 21: | ||

* Can be used as an input or output module. | * Can be used as an input or output module. | ||

* Based around the Lattice MachXO2-256 CPLD | * Based around the Lattice MachXO2-256 CPLD | ||

| + | |||

| + | == Rev. 1 Issues == | ||

| + | * TDI/TDO signals are not connected to the right pins | ||

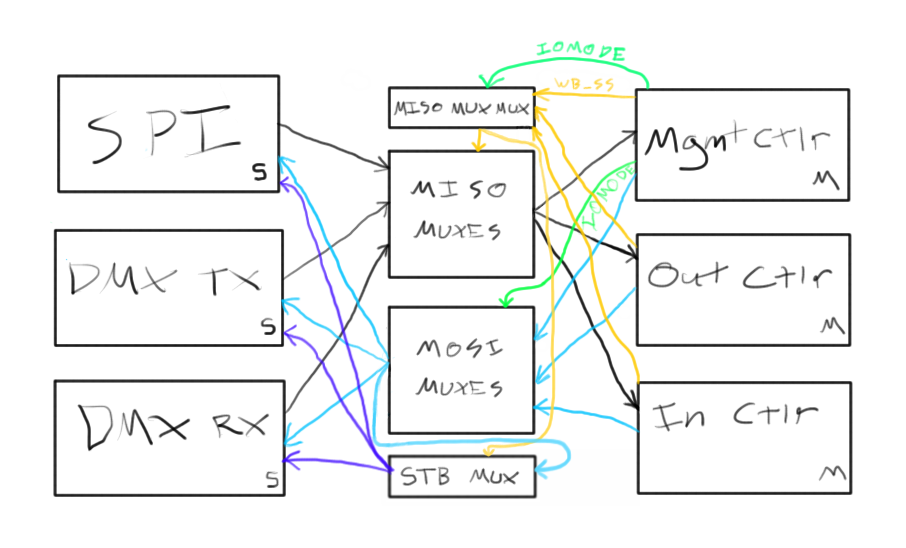

== Architecture == | == Architecture == | ||

| − | + | [[Image:io-dmx_architecture.png]] | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | [[Category: | + | [[Category:Dormant Projects]] |

| − | |||

Latest revision as of 05:07, 9 September 2012

The StrichLux IO-DMX module will provide one universe of DMX for the StrichLux system, and can be used as either an input module or an output module.

Project Status

- 2012-09-09: Putting on hold for now, other modules have priority.

- 2012-05-31: Fixed a bunch of issues introduced in the rearchitecting, transmission now works properly again. Started working on the architecture for the DMX receiver module.

- 2012-05-28: Rearchitected the code to support transmission or reception modules being activated via a series of muxes.

- 2012-05-16: If I disable the tx_en functionality, transmission now fully works! Need to troubleshoot tx_en further, and get reception done.

- 2012-05-01: Still not able to get it working on real hardware. Attempted to get JTAG working, found TDI/TDO pins were connected wrong, green-wired it and can now connect to the chip via JTAG. Will do more troubleshooting tomorrow.

- 2012-04-29: Spent a few hours finding/fixing bugs, simulator now looks really good. Will test on real hardware this week.

- 2012-04-23: Worked more on the code for the CPLD, it's getting stuck somewhere in the state machine and hanging outputting a high level. Need to troubleshoot more in the simulator.

- 2012-04-20: Programmed CPLD and it successfully blinks the status LED green/red! Also started working on the controller code.

- 2012-04-10 - 2012-04-20: Wrote Ruby code to read JEDEC files (ruby-jedec) and program MachXO2 CPLDs via the Bus Pirate

- 2012-04-04: Wishbone interface for DMX transmitter complete, as is mux for sharing the bus between SPI and DMX. Controller is the last Verilog piece pending.

- 2012-04-03: Verilog for DMX transmitter complete and tested in simulator.

- 2012-03-17: Schematic complete and checklist checked, starting and finished board layout/routing, CAM done, submitted to Laen for PCB manufacturing. Parts still need to be ordered.

- 2012-03-15: BOM is complete, schematic almost complete.

- 2012-03-14: Started schematizing/putting BOM together.

Specs

- One universe of DMX, no RDM support at least at the beginning.

- Can be used as an input or output module.

- Based around the Lattice MachXO2-256 CPLD

Rev. 1 Issues

- TDI/TDO signals are not connected to the right pins